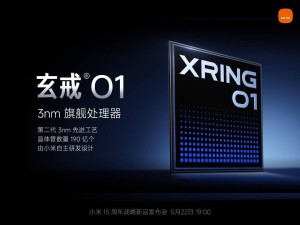

在臺北電腦展(COMPUTEX)的盛大舞臺上,聯發科的首席執行官蔡力行帶來了一則令人振奮的消息。他透露,聯發科即將邁入半導體技術的新紀元,其首款2納米制程芯片預計在今年9月邁入流片階段。與現行的3納米制程相比,這款新芯片預計將實現15%的性能飛躍和25%的功耗削減。

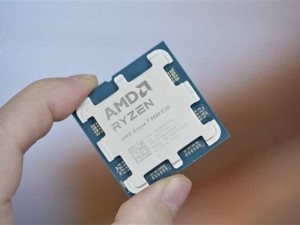

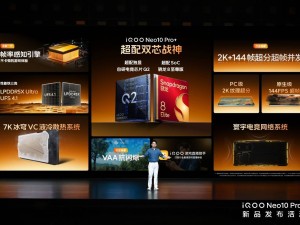

據業界消息,聯發科計劃在今秋推出的天璣9500系列芯片,仍將采用臺積電的3納米制程技術。然而,真正的突破將出現在明年下半年,屆時聯發科將推出采用臺積電2納米工藝的天璣9600系列芯片。這意味著,聯發科有望在全球市場上率先推出2納米制程的芯片產品,領先于蘋果、高通等科技巨頭。

臺積電的2納米制程工藝,采用了革命性的GAAFET(全環繞柵極場效應晶體管)架構。與傳統的FinFET架構相比,GAAFET架構通過創新的納米片結構,實現了柵極材料的完全包裹,從而顯著提升了晶體管的密度,有效降低了漏電現象,使得功耗表現得到了顯著改善。

然而,先進技術的引入也帶來了成本的上升。據業內人士透露,臺積電2納米晶圓的成本將比3納米晶圓高出約10%。這一成本上升將不可避免地傳導至終端產品,尤其是旗艦級智能手機。據悉,芯片成本通常占據手機總成本的20%-30%,因此,2納米芯片的引入可能導致手機售價上漲5%-10%。回顧去年,3納米芯片的推出已使得部分旗艦手機的售價上漲了200-500元,而即將到來的2納米時代,預計價格漲幅將更為顯著。