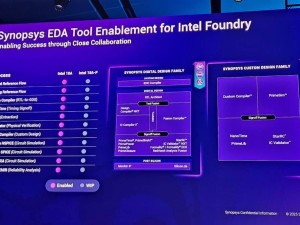

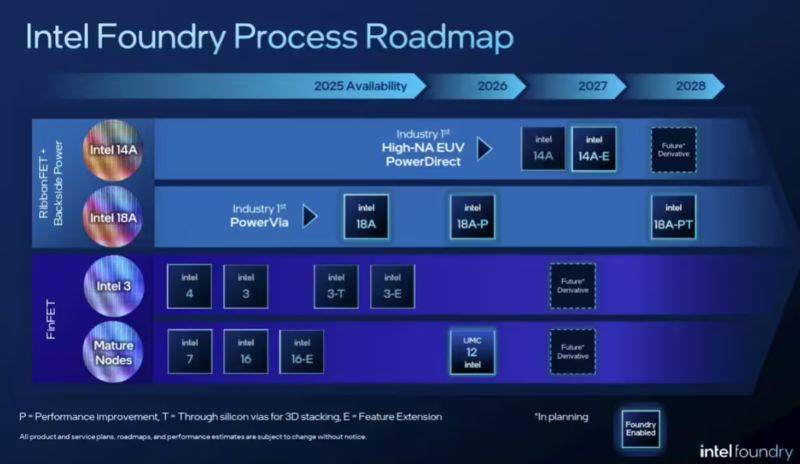

在近期舉辦的Foundry Direct Connect 2025大會上,英特爾新任首席執行官陳立武披露了公司在半導體工藝領域的最新進展。據透露,英特爾的18A工藝節點已成功邁入風險生產階段,預計將于2025年末正式投入量產。與此同時,該工藝的增強版本——18A-P,已在晶圓廠順利運行并產出首批早期晶圓。

陳立武還進一步分享了18A工藝的衍生版本18A-PT的信息。據悉,18A-PT將采用一種名為Foveros Direct的3D堆疊技術,這種技術類似于3D V-Cache,能夠實現垂直晶圓堆疊,從而在關鍵互連密度方面與業界領先者臺積電的產品相抗衡。

英特爾還揭曉了14A工藝節點的最新動態。作為18A的繼任者,14A(等效于1.4納米)預計將于2027年面世,并開創性地采用High-NA EUV光刻技術。與18A相比,14A在能效方面預計將提升15%至20%,芯片密度將增加約30%,同時功耗也將進一步降低。

為了響應市場對先進封裝技術的需求,英特爾代工服務將推出系統級集成服務。該服務將依托Intel 14A和Intel 18A-P制程節點,結合Foveros Direct(3D堆疊)和EMIB(嵌入式多芯片互連橋接)技術,為客戶提供連接解決方案。不僅如此,英特爾還計劃推出多項新的先進封裝技術,包括面向未來高帶寬需求的EMIB-T,以及在Foveros 3D領域的Foveros-R和Foveros-B,為客戶提供更多高效且靈活的選擇。

根據英特爾的官方路線圖,18A-P將于2026年推向市場,而18A-PT則需等到2028年。至于14A節點,則將在2027年到來,并伴隨有14A-E工藝的推出。在行業競爭方面,臺積電的2納米(N2)工藝預計將于2025年下半年量產,性能提升10%至15%,功耗降低25%至30%。值得注意的是,英特爾的14A節點預計將比臺積電同類產品提前一年推出,并且首次采用High-NA EUV技術,這無疑為英特爾在半導體工藝領域的競爭增添了新的籌碼。