在高端計(jì)算芯片領(lǐng)域,隨著性能需求的不斷攀升,芯片尺寸也隨之急劇增大。面對(duì)這一挑戰(zhàn),臺(tái)積電正加速推進(jìn)其創(chuàng)新的CoWoS封裝技術(shù),旨在打造前所未有的巨型芯片。據(jù)透露,該技術(shù)有望將芯片面積擴(kuò)展至接近8000平方毫米,功耗達(dá)到驚人的1000瓦,而其性能則可能比傳統(tǒng)標(biāo)準(zhǔn)處理器高出40倍之多。

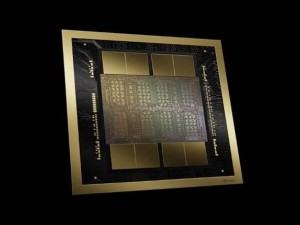

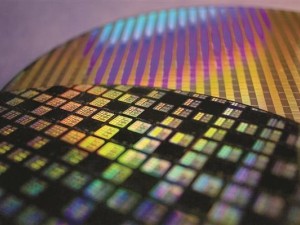

目前,臺(tái)積電CoWoS封裝技術(shù)的中介層面積已經(jīng)能夠突破至2831平方毫米,這一尺寸遠(yuǎn)超臺(tái)積電光罩尺寸的極限,達(dá)到了光罩最大尺寸(約830平方毫米)的3.3倍。這一突破性的進(jìn)展使得像NVIDIA B200和AMD MI300X等高性能芯片得以將大型計(jì)算模塊與多個(gè)HBM內(nèi)存芯片高效整合。

然而,臺(tái)積電的雄心并未止步。據(jù)透露,公司計(jì)劃在不久的將來(lái)推出下一代CoWoS-L封裝技術(shù),該技術(shù)將進(jìn)一步擴(kuò)大中介層面積至4719平方毫米,相當(dāng)于光罩極限尺寸的5.5倍。為了實(shí)現(xiàn)這一目標(biāo),將需要使用面積達(dá)10000平方毫米的大型基板。CoWoS-L還將能夠整合多達(dá)12顆HBM內(nèi)存,包括即將推出的下一代HBM4。

更為驚人的是,臺(tái)積電還展望了未來(lái)中介層面積可能達(dá)到7885平方毫米的愿景,這將是光罩極限尺寸的約9.5倍,并需要面積高達(dá)18000平方毫米的基板。這一前所未有的封裝技術(shù)將能夠容納多達(dá)4顆計(jì)算芯片、12顆HBM內(nèi)存以及其他知識(shí)產(chǎn)權(quán)組件,其尺寸甚至超過(guò)了一個(gè)標(biāo)準(zhǔn)的CD光盤盒。

在封裝技術(shù)不斷突破的同時(shí),臺(tái)積電也在積極應(yīng)對(duì)巨型芯片帶來(lái)的高功耗和高發(fā)熱挑戰(zhàn)。據(jù)預(yù)計(jì),這些巨型芯片的功耗將達(dá)到1000瓦級(jí)別。為了有效管理這一巨大的功耗,臺(tái)積電計(jì)劃在CoWoS-L封裝內(nèi)的RDL中介層上直接集成一顆采用N16工藝和TSV硅通孔技術(shù)制造的電源管理IC。這一創(chuàng)新設(shè)計(jì)將縮短供電距離,減少有源IC數(shù)量,從而降低寄生電阻,提高系統(tǒng)級(jí)供電效率。

在散熱方面,臺(tái)積電也在積極探索直觸式液冷和浸沒(méi)式液冷等高效散熱解決方案,以確保巨型芯片的穩(wěn)定運(yùn)行。

隨著芯片尺寸的增大,現(xiàn)有的OAM模塊形態(tài)也面臨著挑戰(zhàn)。目前,OAM 2.0模塊的尺寸為102×165毫米,而100×100毫米的基板已經(jīng)接近其極限。因此,業(yè)界需要同步制定新的OAM形態(tài)標(biāo)準(zhǔn),以適應(yīng)未來(lái)更大尺寸的芯片封裝需求。

臺(tái)積電在封裝技術(shù)上的持續(xù)創(chuàng)新和突破,不僅展現(xiàn)了其在高端計(jì)算芯片領(lǐng)域的領(lǐng)先地位,也為未來(lái)高性能計(jì)算的發(fā)展奠定了堅(jiān)實(shí)基礎(chǔ)。隨著技術(shù)的不斷進(jìn)步,我們有理由相信,更加高效、強(qiáng)大的巨型芯片將成為可能。