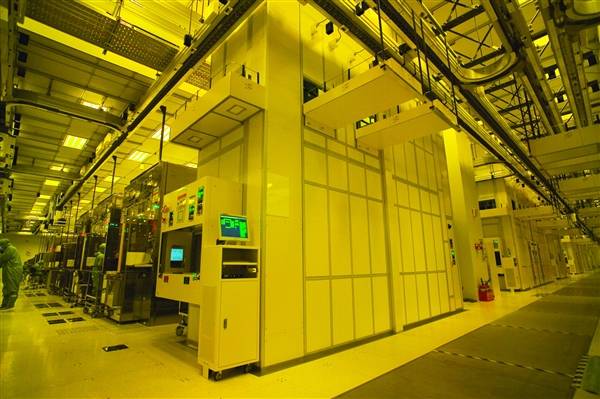

近期,在北美技術論壇這一科技盛會上,臺積電首次披露了其N2 2nm工藝的關鍵性能指標——缺陷率(D0)的最新進展。據悉,N2工藝的缺陷率表現遠超之前的7nm、5nm及3nm等先進制程。

盡管臺積電并未透露具體的缺陷率數據,但通過對比不同工藝缺陷率隨時間變化的趨勢圖,可以清晰地看到N2工藝的優勢所在。這一趨勢圖展示了從早期試產到接近量產階段,各工藝缺陷率的演變情況。

值得注意的是,N2工藝首次采用了GAAFET全環繞晶體管技術,這一創新為臺積電在半導體制造領域樹立了新的里程碑。目前,N2工藝距離大規模量產還有兩個季度的時間,預計將在今年年底正式投產。

在N2工藝的近兩個月試產期間,其缺陷率表現與同期的N5/N4工藝相當,甚至略勝一籌。與更早的N7/N6以及N3/N3P工藝相比,N2的缺陷率更是顯著更優。從歷史數據來看,N7/N6工藝在試產到量產的半年內,綜合缺陷率一直居高不下;而N3/N3P工藝從量產初期就展現出了較低的缺陷率;N5/N4工藝則更為出色,從試產階段就保持了較低的缺陷率水平。

若N2工藝能夠延續N5/N4的優異表現,其市場前景無疑將十分廣闊。臺積電方面還指出,工藝的缺陷率能否迅速降低,不僅取決于工藝本身的設計和技術水平,還與芯片制造數量和產能規模密切相關。大規模的芯片生產能夠更容易地發現并改進缺陷,從而提升整體工藝質量。

事實上,臺積電在N2工藝上已經流片了數量可觀的芯片,這也是其能夠快速降低缺陷率的關鍵因素之一。通過不斷的試驗和改進,臺積電正穩步邁向2nm工藝的大規模量產。